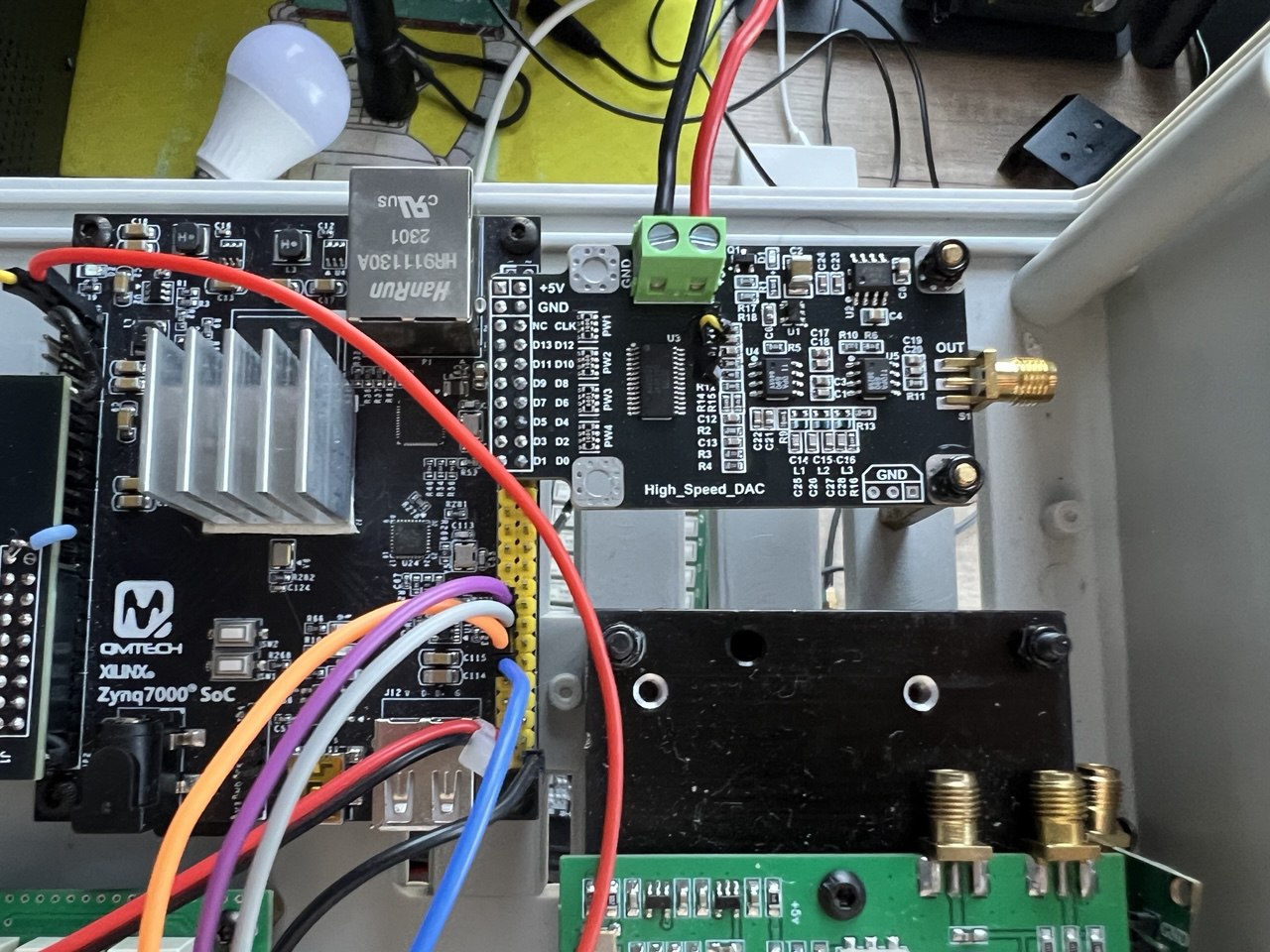

Conditions:

Bad NoName generators (waiting CCHD-950)

First revision ADC board on qmtech (waiting for 4th revision from nextpcb)

Clock on the antminer connected directly to the antminer board and ADC.

On both systems DAC clock has 90 degrees phase shift.

So in future result will be improved, this is the start point.

Analog voltage 3.3v

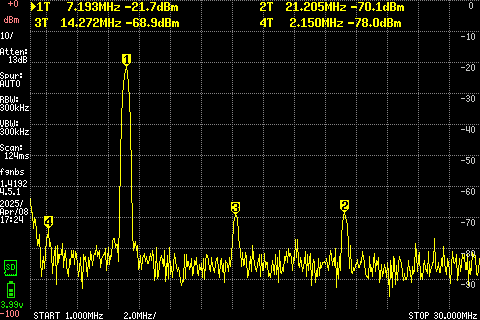

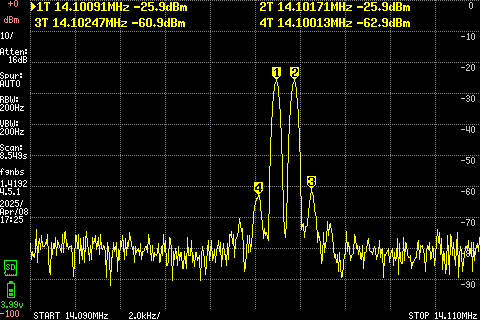

QMTECH:

~44dbc SFDR

~36dbc IMD3 (42dbc PEP)

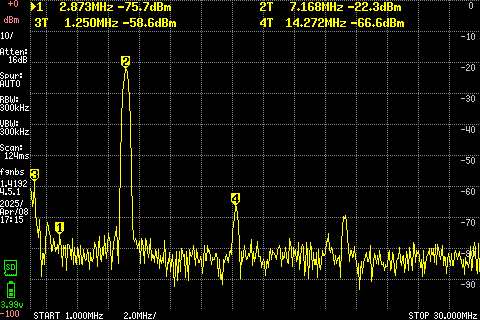

ANT:

~47dbc SFDR

~36dbc IMD3 (~42dbc PEP)