Just some old photos 🙂

It’s using FPGA firmware based on Openhpsdr project with modifications by EU1SW.

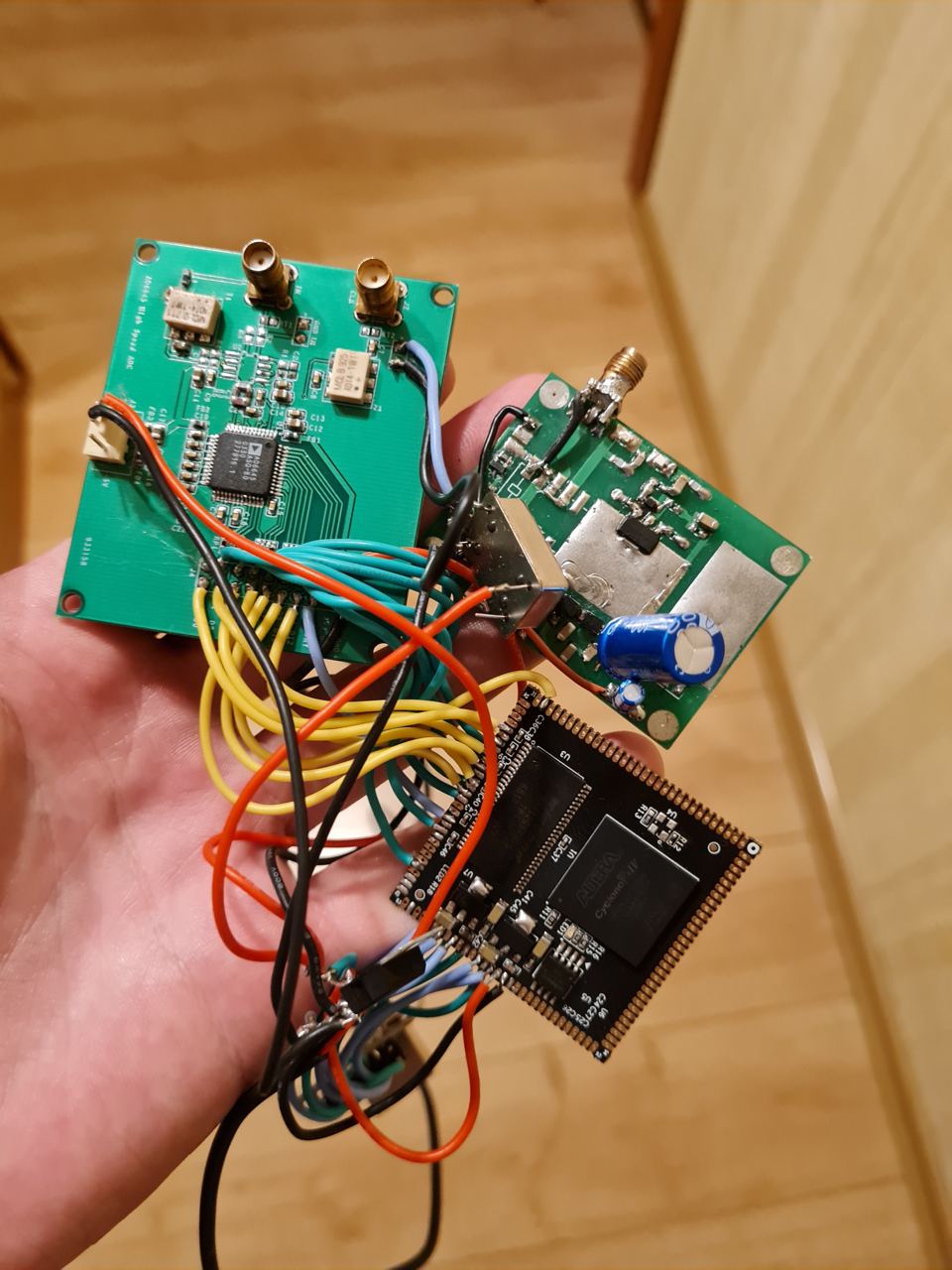

I started with AD9226 dual 12bit SDR receiver and ended with something like this:

Horrible 🙂 But it was first experience with huge lack of knowledge.

It had Cyclone 4 FPGA with Hermes compatible network protocol, DAC904E as DAC and BFG591 as preamp.

Somehow it was working, not as it should, but at least it was enabling and receiving something.

Some videos:

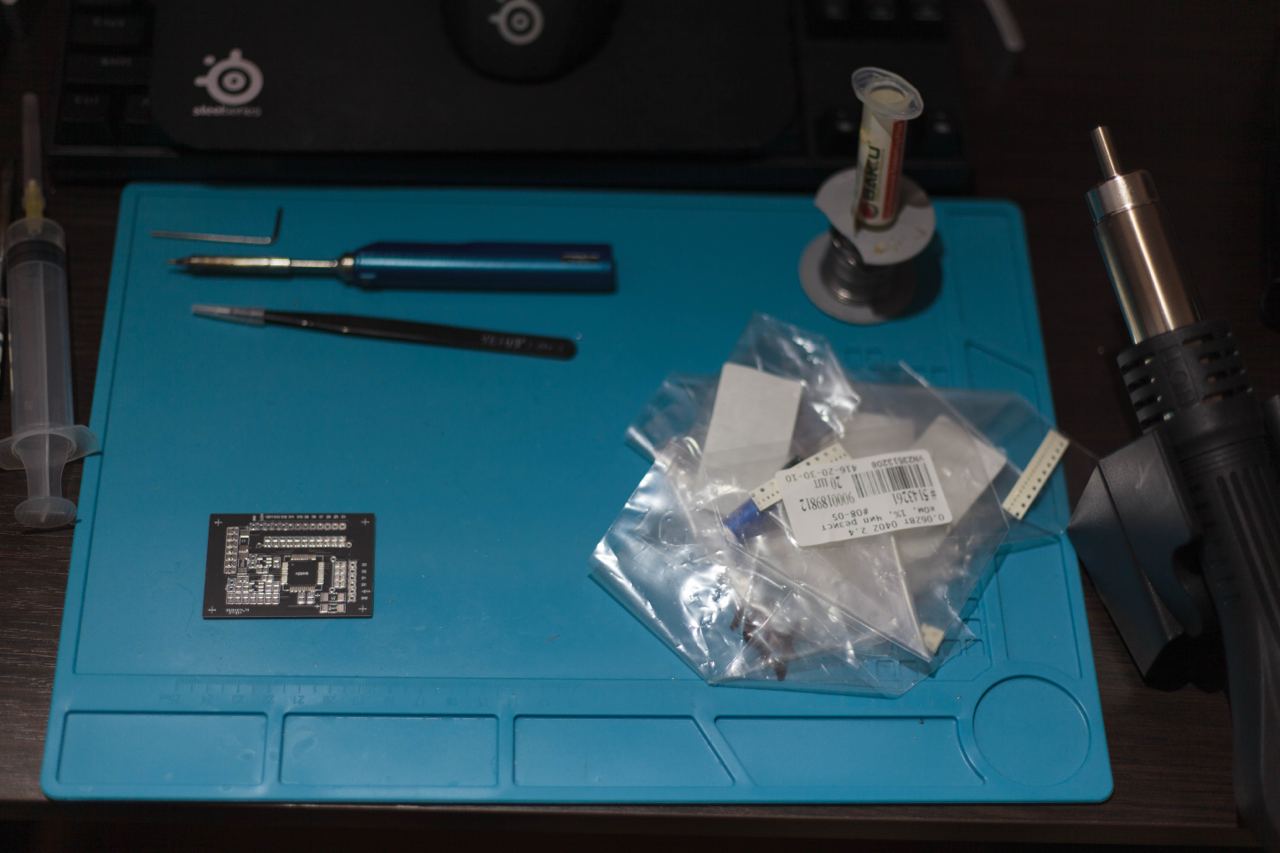

And at the same time I was assembling pretty the same but with AD6645 ADC and FPGA in different package:

Also I built different module for ADC:

Also old video from 2018 — first transceiver (ad9226) + PiHPSDR:

The same as in first photos but without case and with raspberry pi.