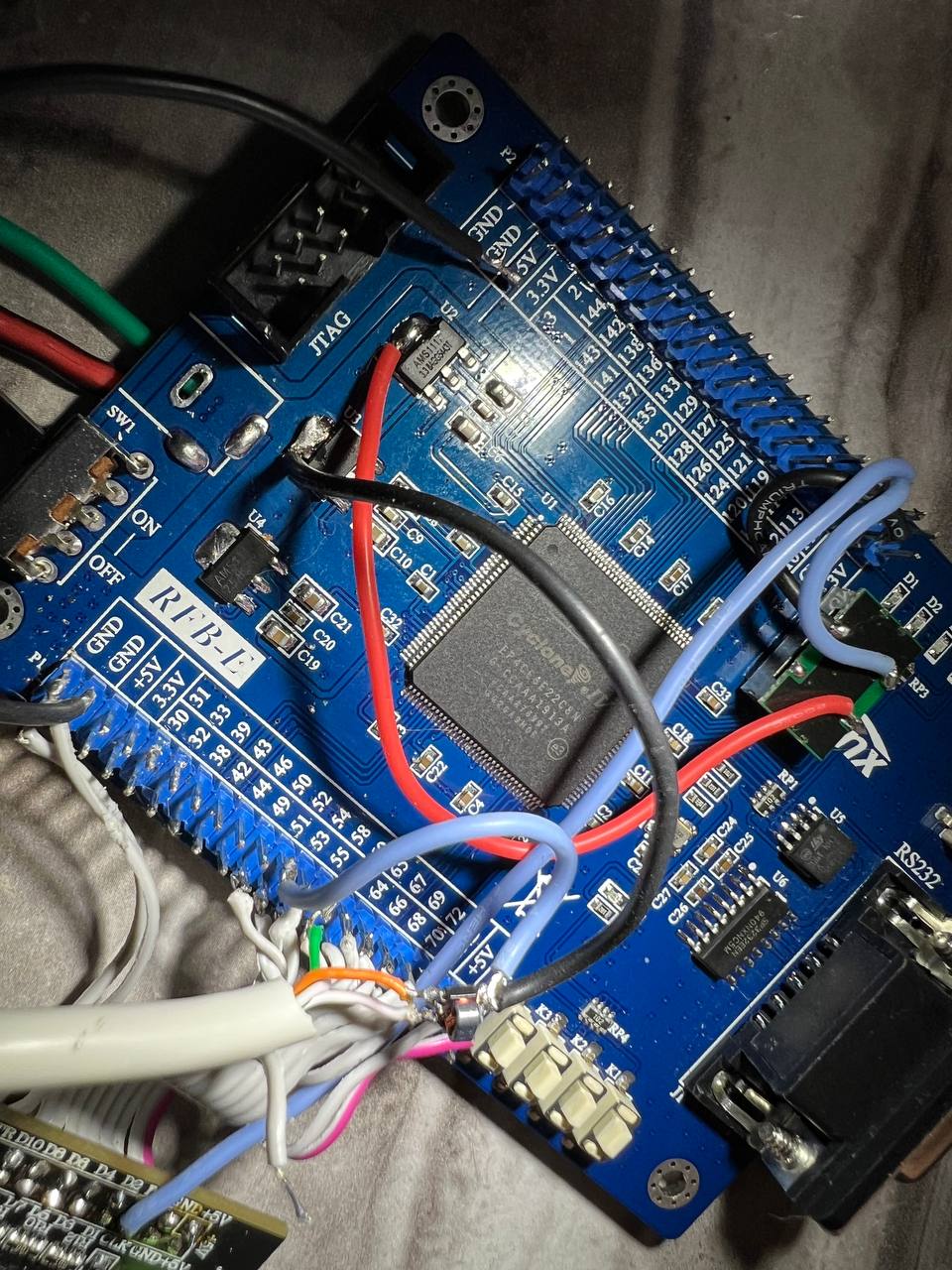

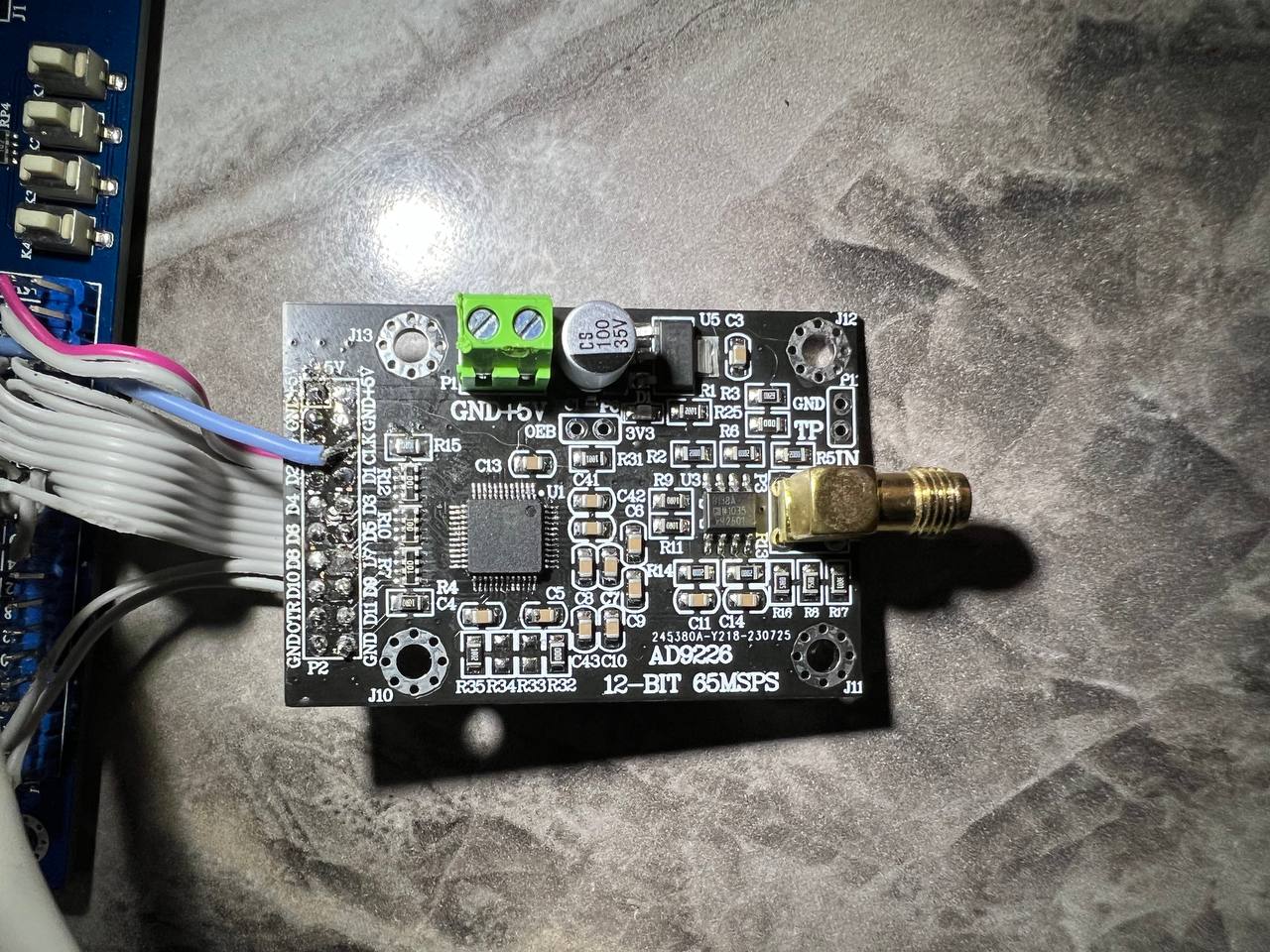

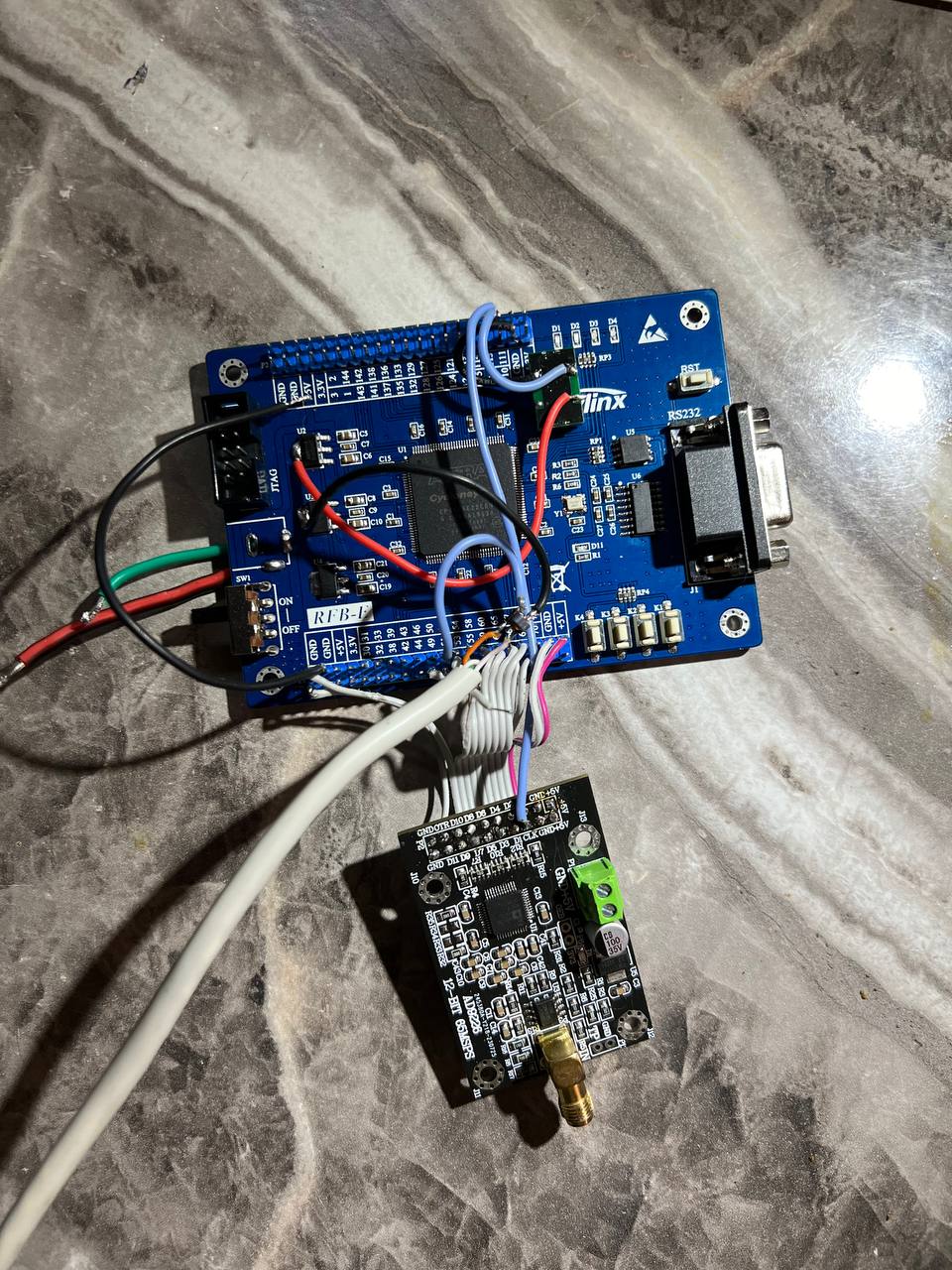

Used parts: Stock AD9226 demoboard + Cyclone 4 EP4CE6 devboard + ABLNO 96MHZ clock generator + 1:1 transformer for RX pair.

Receiving data from ADC at 96MHz external clock negedge (no ADC ready for this ADC). ADC uses 96MHz clock directly. Ethernet TX pair directly on FPGA pins, RX via 1:1 transformer, one output pin on the 1.2V linear stabiliser, second on the FPGA I/O pin.